|

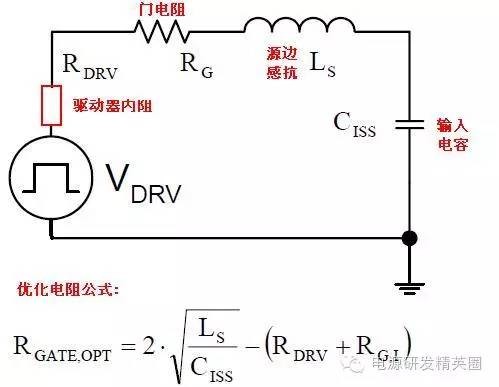

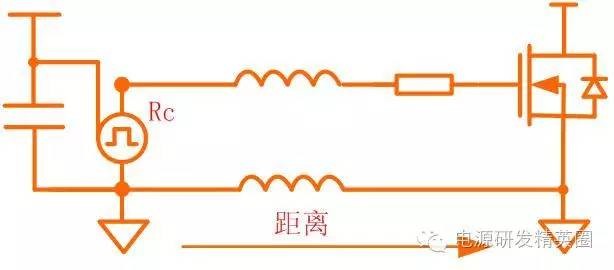

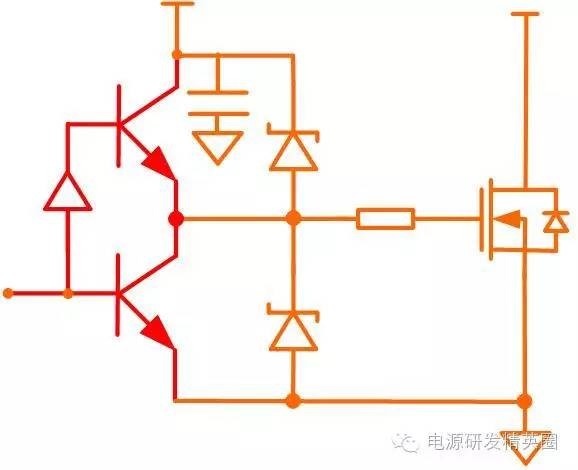

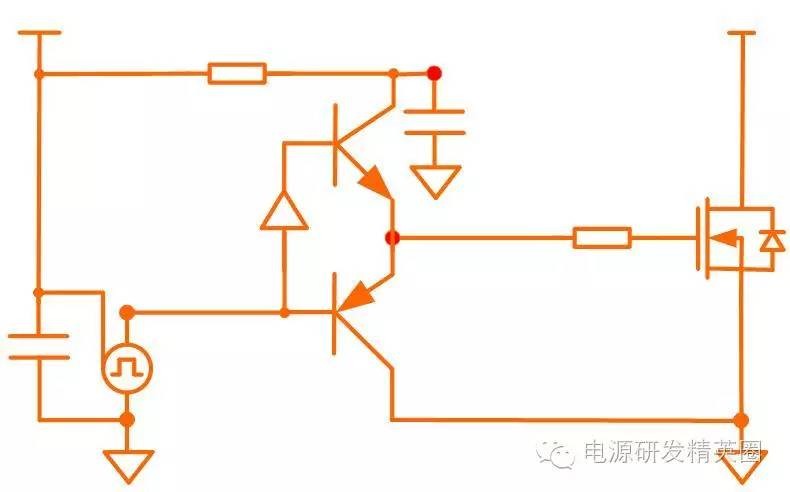

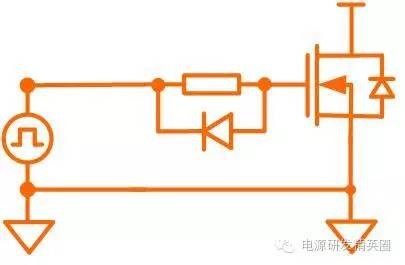

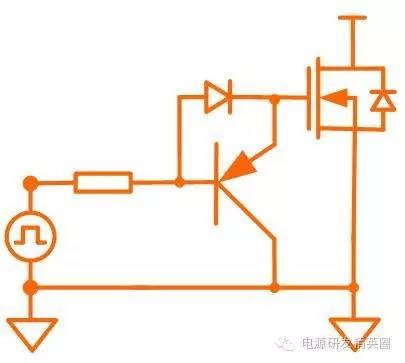

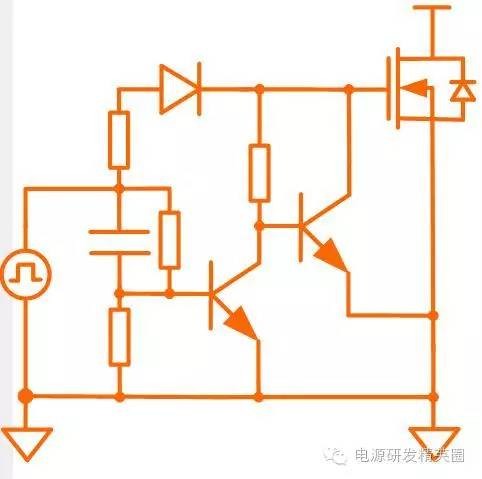

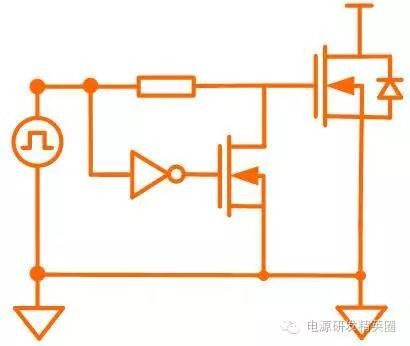

我们在应用MOS管和设计MOS管驱动的时候,有很多寄生参数,其中最影响MOS管开关性能的是源边感抗。寄生的源边感抗主要有两种来源,第一个就是晶圆DIE和封装之间的Bonding线的感抗,另外一个就是源边引脚到地的PCB走线的感抗(地是作为驱动电路的旁路电容和电源网络滤波网的返回路径)。在某些情况下,加入测量电流的小电阻也可能产生额外的感抗。我们分析一下源边感抗带来的影响:1.使得MOS管的开启延迟和关断延迟增加由于存在源边电感,在开启和关段初期,电流的变化被拽了,使得充电和放电的时间变长了。同时源感抗和等效输入电容之间会发生谐振(这个谐振是由于驱动电压的快速变压形成的,也是我们在 G端看到震荡尖峰的原因),我们加入的门电阻Rg和内部的栅极电阻Rm都会抑制这个震荡(震荡的Q值非常高)。  我们需要加入的优化电阻的值可以通过上述的公式选取,如果电阻过大则会引起G端电压的过冲(优点是加快了开启的过程),电阻过小则会使得开启过程变得很慢,加大了开启的时间(虽然G端电压会被抑制)。 园感抗另外一个影响是阻碍Id的变化,当开启的时候,初始时di/dt偏大,因此在原感抗上产生了较大压降,从而使得源点点位抬高,使得Vg电压大部分加在电感上面,因此使得G点的电压变化减小,进而形成了一种平衡(负反馈系统)。另外一个重要的寄生参数是漏极的感抗,主要是有内部的封装电感以及连接的电感所组成。在开启状态的时候Ld起到了很好的作用(Subber吸收的作用),开启的时候由于Ld的作用,有效的限制了di/dt/(同时减少了开启的功耗)。在关断的时候,由于Ld的作用,Vds电压形成明显的下冲(负压)并显著的增加了关断时候的功耗。下面谈一下驱动(直连或耦合的)的一些重要特性和典型环节:直连电路最大挑战是优化布局实际上驱动器和MOS管一般离开很远,因此在源级到返回路径的环路上存在很大的感抗,即使我们考虑使用地平面,那么我们仍旧需要一段很粗的PCB线连接源级和地平面。  另外一个问题是大部分的集成芯片的输出电流都比较小,因为由于控制频率较高,晶圆大小受到限制。同时内部功耗很高也导致了IC的成本较高,因此我们需要一些扩展分立的电路。 旁路电容的大小由于开启的瞬间,MOS管需要吸取大量的电流,因此旁路电容需要尽可能的贴近驱动器电源端。有两个电流需要我们去考虑:第一个是驱动器静态电流,它收到输入状态的影响。他可以产生一个和占空比相关的纹波。另外一个是G极电流,MOS管开通的时候,充电电流时将旁路电流的能量传输至MOS管输入电容上。其纹波大小可用公式来表明,最后两个可合在一起。驱动器保护  这是最便宜和有效地驱动方式,此电路需要尽量考虑MOS管,这样可以使得开启时大电流环路尽可能小,并且此电路需要专门的旁路电容。  这是最简单的加速电路。Rgate调整着MOS管的开启速度,当关断的时候,由二极管短路电阻,此时G极电流最小为:Imin=Vf   优点和上面的PNP管子相同,缺点是加入了一个反向器,加入反向器势必会造成延迟。

|